从MCU到FPGA:第1部分

我是MCU的长期用户和狂热者,特别是对多功能低成本MCU上有着浓厚的兴趣,这种MCU模块能够通过单芯片实现优秀的通信能力。我做过很多有意思的小玩意,包括:MP3播放器、闹钟、无线地面湿度控制系统、宠物活动监视器、低功耗蓝牙姿态控制等。在这些小项目中,MCU实现信息的收集和传输,用起来十分方便。

最近,我接手一个项目,这个项目不仅要求我使用FPGA,而且还要求我使用功能更强大的ARM。这都是我从未接触过的领域。在这个系列博客中,我将介绍我是如何将自己现有的MCU知识和经验运用到FPGA中的。本文是系列博客的在第一篇,我将从FPGA的优点和缺点入手,并介绍Terasic DE10 Nano开发套件,以及IP核在FPGA设计中的作用。

关于FPGA

如果你开发的项目一直与MCU有关,你一定会发现MCU的学习曲线并不陡峭,所用的开发工具都可以轻易获得,开发和调试的过程简单,设计很容易上手。不过,你也会发现,MCU在处理复杂事务、运行速度和接口的多样性上是很有限的。我个人所经历的项目,由于功能既不复杂,也没有重要的处理需求,因此,一直以来MCU是很理想的选择。

FPGA是包含可编程逻辑元件(LE)的集成电路,其可编程单元已经内置在芯片中,功能十分灵活。

例如,他们可以通过编程作为加速器或RAM来提高系统性能,可以通过编程实现新的标准或算法,也可以根据需求添加各种通信接口,所有的这些都有助于降低系统成本并延长产品生命周期。但这种设计的缺点是学习曲线非常陡峭,对于MCU开发人员来说,在刚刚学习FPGA的时候,因IO端口和编码方式的变化,学习起来还是很困难的。对于MCU来说,在同一时刻,只能实现一个或一组IO的翻转,并且所有的IO只有一个电压标准。而FPGA的IO是并行处理的,并且不同bank的IO可以遵循不同电压标准。

幸运的是,我发现了Intel Cyclone V SoC DE10 Nano开发套件。英特尔Cyclone V SoC将FPGA与双核ARM Cortex A9结合,允许使用多种方式配置FPGA,开发套件包含显示和通信端口、按钮和开关、引脚映射和快速配置工具、JTAG调试器以及来自Terasic和Intel的文档说明和指南。

规划FPGA开发

在规划MCU开发的时候,我们首先确定需要哪些接口,如SPI,I2C,Wi-Fi等,然后根据MCU的电压,引脚数量,提供的通信接口,支持的库和价格作出MCU的选型。在使用FPGA的时候,所有的通信接口都是依靠编程来实现的,因此无需考虑通信接口的限制。其限制因素是逻辑单元的数量,因为所需要的端口,软核或存储器单元都是基于这些逻辑单元创建的。因此,需要做权衡的是,逻辑单元数目越大,FPGA的能力越强,其成本也越高。虽然FPGA通常具有较高的初始成本,但由于它们可以实现多个芯片组件的功能,并且还能够节省大量板上空间,所以综合来看其成本并不高。

我发现自己正处在一个关键时刻:我要如何确定我的设计需要多少逻辑单元?

答案是,这取决于对IP核的需求,IP核由协议、功能、代码以及外部模块执行的特定任务组成。几乎所有的FPGA都是由逻辑单元LE,寄存器和I / O bank组成。具体来说:

逻辑单元LE是可编程的,是FPGA内部的门阵列,每一个逻辑单元都具有一定数量的查找表,触发器和多路复用器。

寄存器是一组触发器,能够保存数据并实现诸如定时器等功能。

I / O bank是一组连接外部电路的输入/输出引脚。每个bank都有一个独立的电压标准,并且有电流大小的限制。

最初我并没有意识到IP核的重要性,因为我还没有领会到这样一个事实:IP核实现了一种能够代替物理设备的能力,这些设备包括MCU、通信控制器或者其他一些我会使用另一个芯片实现的东西。

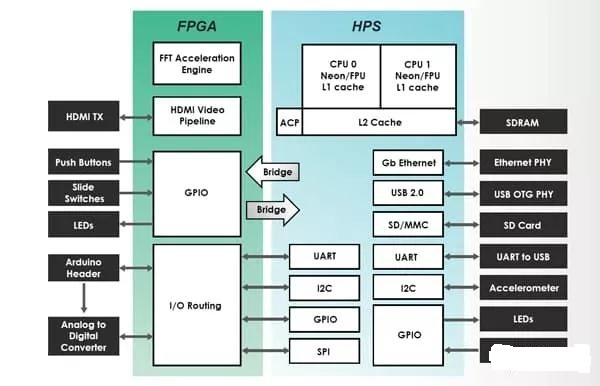

如图1所示,Cyclone V 包含FPGA层和HPS层,在DE10 Nano上FPGA层主要用作低延迟的I/O扩展。所有这一切体现了FPGA的另一个设计特点:它可以在单个芯片上实现多个PCB板上芯片的功能,从而,使得后续的设计更加灵活。

图1:Terasic DE10 Nano Cyclone V FPGA和硬件处理器系统(HPS)的接口布局。

大部分低级I / O端口通过FPGA进行控制和连接,这就降低了CPU等待低级别I/O端口的时间,同时也允许数据在传递到HPS之前进行相应的处理或调整。

这是一种多么完美的设计,Cyclone V FPGA的接口可扩展,而且能够实现加速器的功能,这种设计架构提高了HPS层的处理能力。在这种情况下,正如图2所示,HDMI接口是非HPS本地接口,因此用作HDMI的MCU资源并不多。

图2:FPGA和HPS的接口布局

HDMI的输出在FPGA上运行,这降低CPU负载并添加了非本地接口;

存在一个OpenCV加速示例,这是为了体现两种类型处理器结合的优势;

Terasic已经实现了基本的通信功能范例,并且有一个预定义的引脚映射列表,该列表定义了电压和电流限制。

总的来说,我很喜欢FPGA,并且对它的扩展和加速功能十分感兴趣。不过,我也想知道他们到底有哪些局限性。他们能运行到高的频率?他们可以支持哪些协议?他们会消耗多少LE?总的来说,IDE比我用过的其他软件更简单,并且包含了令人惊叹的文档。硬件似乎非常强大,现在我正在设计一个项目,这个项目能够测试板上的硬件限制。

下一篇:从MCU到FPGA:第2部分

- 如何保证出行服务过程中的安全?[18年05月20日 10:01]

- 特斯拉事故连连,静止车辆难以被识别?[18年05月20日 10:00]

- 豪车劳斯莱斯也要电动化了?[18年05月20日 09:58]

- 捡现成的,传苹果可能出资收购特斯拉[18年05月20日 10:00]

- 一切为了产能,特斯拉落户上海浦东[18年05月20日 09:59]

- 特斯拉“入华”新进展,超级工厂能来中国吗?[18年05月20日 09:59]

在线客服

在线客服